# **Uni-directional ESD Protection Diode**

## DESCRIPTIONS

The TESDL3V3U1051M5 is uni-directional ESD rated clamping cell to protect power interfaces, or one control line, or one low speed data line in an electronic system. It has been specifically designed to protect sensitive electronic components which are connected to power and control lines from over-voltage damage by Electrostatic Discharging (ESD), and Lightning.

TESDL3V3U1051M5 is a unique design which includes proprietary clamping cells in a small package.

During transient conditions, the proprietary clamping cells prevent over-voltage on the control/data/power lines, protecting any downstream components.

The TESDL3V3U1051M5 may be used to provide ESD protection up to  $\pm$ 30kV (contact and air discharge) according to IEC61000-4-2, and withstand peak pulse current up to 11.2A (8/20µs) according to IEC61000-4-5.

## FEATURES

- ESD protect for 1 line with bidirectional

- Provide ESD protection for each channel to IEC 61000-4-2 (ESD) ±30kV (air), ±30kV (contact) IEC 61000-4-5 (Lightning) 11.2A (8/20us)

- Suitable for 3.3V and below, operating voltage applications

- Small package saves board space

- Protect one I/O line or one power line

- Fast response time

- Low leakage

- RoHS Compliant

- Halogen-Free according to IEC 61249-2-21

## APPLICATION

- Computers and peripherals

- Power supply protection

- Portable devices

- Notebooks, desktops, and servers

| PACKAGE: SOD-523F | PIN CONFIG | URATION | CIRCUIT DIAGRAM |

|-------------------|------------|---------|-----------------|

| Ŀſ                |            | PIN2    |                 |

|                   | PIN 1      | Cathode |                 |

|                   | PIN 2      | Anode   |                 |

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C unless otherwise noted) |                  |             |      |  |  |

|-------------------------------------------------------------------------|------------------|-------------|------|--|--|

| PARAMETER                                                               | SYMBOL           | VALUE       | UNIT |  |  |

| Peak pulse power (tp = 8/20us)                                          | P <sub>PK</sub>  | 158         | W    |  |  |

| Peak pulse current (tp = 8/20us)                                        | I <sub>PP</sub>  | 11.2        | А    |  |  |

| ESD according to IEC61000-4-2 air discharge                             | V                | ±30         | kV   |  |  |

| ESD according to IEC61000-4-2 contact discharge                         |                  | ±30         | kV   |  |  |

| Operating junction temperature range                                    | TJ               | -55 to +150 | °C   |  |  |

| Storage temperature range                                               | T <sub>STG</sub> | -55 to +150 | °C   |  |  |

## **ELECTRICAL SPECIFICATIONS** ( $T_A = 25^{\circ}C$ unless otherwise noted)

| PARAMETER                         | CONDITIONS                            | SYMBOL           | MIN | ТҮР  | MAX  | UNIT |

|-----------------------------------|---------------------------------------|------------------|-----|------|------|------|

| Reverse working voltage           |                                       | V <sub>RWM</sub> | -   | -    | 3.3  | V    |

| Reverse breakdown voltage         | $I_{R} = 1mA, T_{J} = 25^{\circ}C$    | V <sub>BR</sub>  | 5   | -    | -    | V    |

| Reverse leakage current           | $V_{RWM} = 3.3V, T_{J} = 25^{\circ}C$ | I <sub>R</sub>   | -   | -    | 50   | nA   |

| Clamping voltage <sup>(1)</sup>   | $I_{PP} = 5A$ , tp = 8/20us           | Vc               | -   | 8.4  | -    | V    |

|                                   | $I_{PP} = 11.2A$ , tp = 8/20us        |                  | -   | -    | 14.1 | V    |

| Clamping voltage <sup>(2)</sup>   | $I_{TLP} = 16A$ , tp = 100ns          | V <sub>CL</sub>  | -   | 11.3 | -    | V    |

| Junction capacitance              | $1MHz, V_R = 0V$                      | CJ               | -   | 116  | -    | pF   |

| Dynamic resistance <sup>(2)</sup> |                                       | R <sub>DYN</sub> | -   | 0.24 | -    | Ω    |

#### Notes:

AIWAN

CONDUCTOR

Non-repetitive current pulse, according to IEC61000-4-5. 1.

2. TLP parameter: Z0 = 50  $\Omega$ , tp = 100ns, tr = 2ns, averaging window from 60ns to 80ns. RDYN is calculated from 4A to 16A.

| ORDERING INFORMATION  |          |                        |  |  |  |

|-----------------------|----------|------------------------|--|--|--|

| ORDERING CODE PACKAGE |          | PACKING                |  |  |  |

| TESDL3V3U1051M5 RKG   | SOD-523F | 3,000 / 7" Tape & Reel |  |  |  |

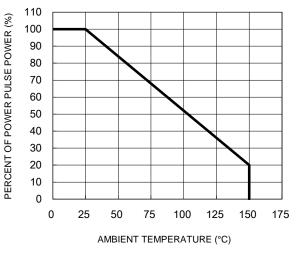

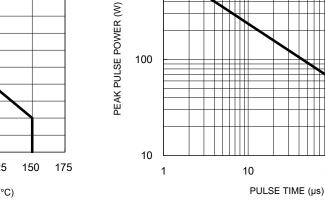

## **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

#### Fig.1 Peak Pulse Power vs. Junction Temperature Fig.2 Non-Repetitive Peak Pulse Power vs. Pulse Time

1000

100

Fig.3 Clamping Voltage vs. Peak Pulse Current

Fig.4 Capacitance vs. Reverse Voltage

100

1000

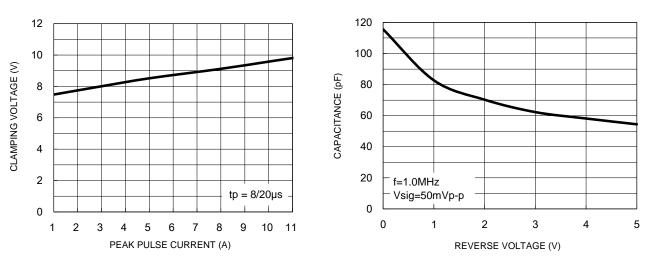

## **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

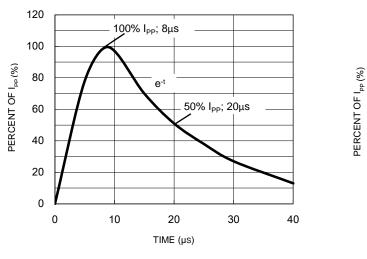

#### Fig.6 8/20µs pulse waveform

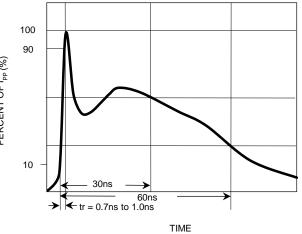

Fig.7 ESD pulse waveform

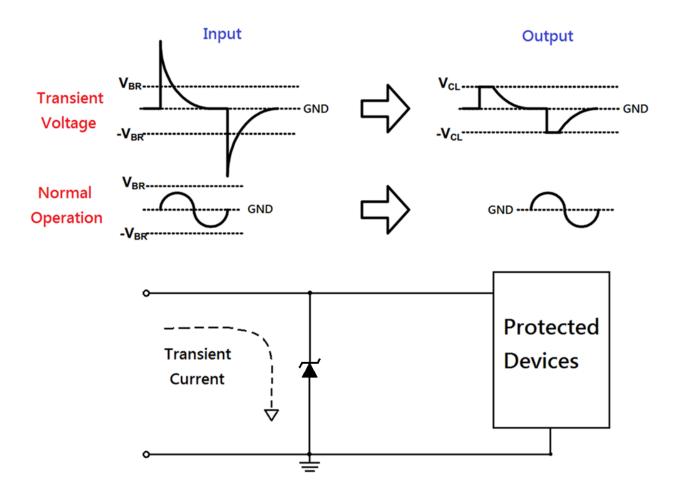

## **APPLICATION INFORMATION**

#### **Device Connection**

The TESDL3V3U1051M5 is designed to protect one line against system ESD Lightning pulses by clamping it to an acceptable reference. It provides bidirectional protection.

The usage of the TESDL3V3U1051M5 is shown in Fig1.Protected line, such as data line, control line, or power line. In order to minimize parasitic inductance in the board traces, all path lengths connected to the pins of TESDL3V3U1051M5 should be kept as short as possible.

In order to obtain enough suppression of ESD induced transient, good circuit board is critical. Thus, the following guidelines are recommended:

- Let the path length between the protected lines and the TESDL3V3U1051M5 minimize.

- Place the TESDL3V3U1051M5 near the input terminals or connectors to restrict transient coupling.

- The ESD current return path to ground should be kept as short as possible.

- Use ground planes whenever possible.

## Fig.1 ESD protection by TESDL3V3U1051M5

Taiwan Semiconductor

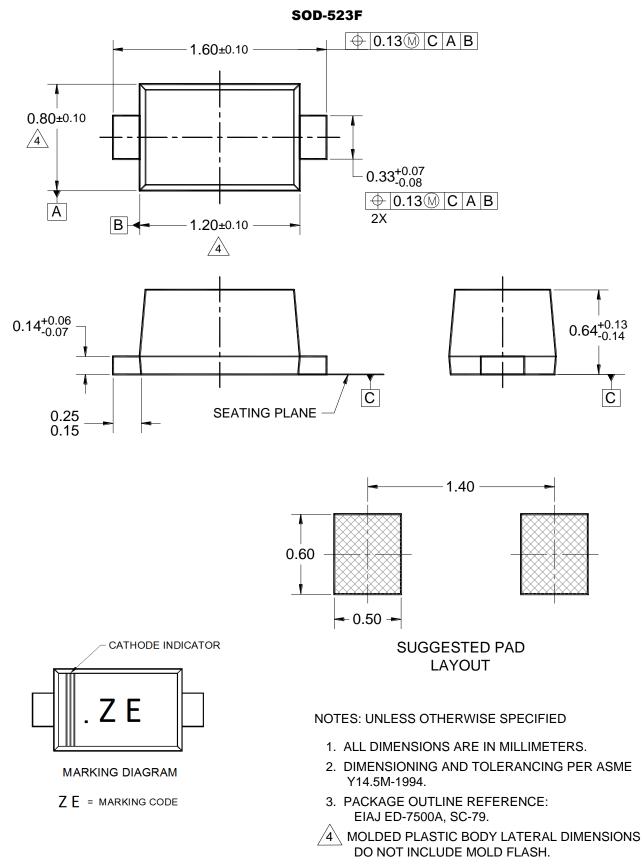

## PACKAGE OUTLINE DIMENSIONS

5. DWG NO. REF: HQ2SD07-SOD523F-047 REV A.